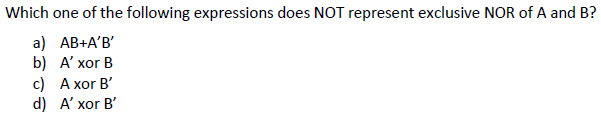

Ans:a

Think, Analyze and Implement

Wow! Look In

Hmmm! That's a Cool Deal!

Technical hubbies

Yahoo!!!

Recent Posts

Popular Posts

-

Antenna Fundamentals 1)A cell tower antenna needs to cover an area with 120° angular coverage in horizontal plane. The radiation patt...

-

MULTIPLE CHOICE QUESTIONS ON “INTRODUCTION TO 8086” 1. The first micro-processor had a (n) ______. a) 1-bit data bus b) 2- bit da...

-

This post gives you complete information regarding practical implementation of Microwave and Optical Communications. The requirements, proc...

-

1. Why interoperability is required in Internet of Things? a. Heterogeneous wireless communication protocols b. Different programming la...

-

Answers are at end........... 1. Ans: 1 point 2. Ans: 1 point 3. Ans: 1 point 4. ...

-

MULTIPLE CHOICE QUESTIONS ON “SIGNAL DESCRIPTIONS OF 8086” 1. The clock rate of microprocessor 8086 is _________. a) 5 MHZ b) 8 M...

-

1. a) b) c) d) Ans:a 2. a) b) c) d) Ans: b 3. a) b) c...

-

Sorry for last time wrong answer for Question 2. Just overlooked the question. Even I did the same mistake. If you sense any wrong answe...

-

1. Protocol used for connection less socket programming: a. TCP b. UDP c. Both d. None Ans : b 2. Which one is an SDN c...

-

This post gives you information regarding Very Large Scale Integration (VLSI) laboratory, which was recently added to B.tech students of JN...

Some answers are incorrect.

ReplyDeleteand these are the correct answers for that,

QUESTION 1:

Consider a 4-bit adder with inputs A = {A3A2A1A0} and B = { B 3 B 2 B 1 B 0}. For which of the following

input condition no carry-out would be generated. (Assume there is no carry input)

a. A = {1011}, B = {0101}

b. A = {1011}, B = {0001}

c. A = {1011}, B = {0100}

d. A = {1001}, B = {0101}

Correct Answer: a

Detailed Solution:

Carry out would be generated only for first option. Sum = 10000

QUESTION 8:

In a half-subtractor circuit with X and Y as inputs, the Borrow (M) and Difference (N = X - Y) are given by

a) M = XY, N = X xor Y

b) M = X’Y, N = X’ xor Y

c) M = X’Y, N = X xor Y

d) M = X’Y, N = (X xor Y)’

Correct Answer: c

Detailed Solution:

M = X’Y, N = X xor Y

QUESTION 9:

If the output of a digital circuit makes a momentary transition to logic 1, while otherwise the output is

logic 0, it is called a

a) Static-1 Hazard

b) Static-0 Hazard

c) Dynamic Hazard

d) No Hazard

Correct Answer: b

QUESTION 10:

A full adder can be realized using

a) one half adder, two AND gates

b) two half adders, one OR gate

c) two half adders, one AND gate

d) two half adders, two AND gates

Correct Answer: b